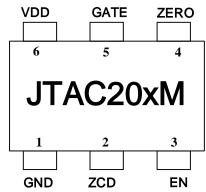

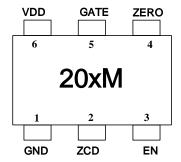

## **Pin Distribution and Description**

| Number | Name | Description                          |

|--------|------|--------------------------------------|

| 1      | GND  | Ground terminal                      |

| 2      | ZCD  | Zero-crossing detection terminal     |

| 3      | EN   | Enable-control terminal              |

| 4      | ZERO | Zero-crossing signal output terminal |

| 5      | GATE | G pole                               |

| 7      | VDD  | Power supply terminal T1 pole        |

# **Maximum Rating**

| Parameter                                      | Range                |

|------------------------------------------------|----------------------|

| VDD GATE voltage                               | V <sub>OVP</sub> -1V |

| ZCD EN ZERO voltage                            | -0.3 V~ 5.5V         |

| min./max. junction temperature TJ              | -40 ~ 150            |

| min./max. ambient temperature TA               | -40 ~ 85             |

| min./max. storage temperature Tstg             | -55 ~ 150            |

| soldering temperature (soldering tin, 10secs ) | 260                  |

| VDD voltage range recommended                  | -0.3V ~ 15V          |

$(V_{DD}=6V, T_A$  • unless otherwise specified)

| Symbol                        | Parameter                              | <b>Test Condition</b> | MIN. | TYP. | MAX. | Unit |

|-------------------------------|----------------------------------------|-----------------------|------|------|------|------|

| Supply volta                  | ge (VDD voltage)                       |                       |      |      |      |      |

| I <sub>Start-up</sub>         | Start-up current                       | V <sub>DD</sub> =3V   |      | 350  |      | μΑ   |

| I <sub>Static</sub>           | Static current                         | V <sub>DD</sub> =5.5V |      | 800  |      | μΑ   |

| UVLO <sub>(ON)</sub>          | Under-voltage lockout <sub>(ON)</sub>  | VDD voltage drop      |      | 3.5  |      | V    |

| UVLO <sub>(OFF)</sub>         | Under-voltage lockout <sub>(OFF)</sub> | VDD voltage rise      |      | 4    |      | V    |

| V <sub>DD-OP</sub>            | Power supply operating voltage range   |                       | 4.8  | 5    | 6.5  | V    |

| OVP                           | Overvoltage protection voltage         |                       | 16   | 18   | 20   | V    |

| V <sub>DD-max</sub>           | Clamping voltage                       |                       | 18   | 20   | 22   | V    |

| Zero-crossing detection (ZCD) |                                        |                       |      |      |      |      |

### **Functional Mode Description**

To meet the needs of different customers, JTAC20xM is designed to work under three modes. The connection relationship and functional mode sequence diagram are as follows.

#### **1** Mode 1

The chip uses common power supply mode, ZCD is connected to AC power line or load terminal through resistance. The pin is used for zero-crossing detection. MCU always outputs high power level to enable chip EN, or EN directly connects to high power level. At each zero-crossing of the chip, ZERO outputs the signal (1.2ms square wave), while the GATE outputs the driving signal (6 cycles of 200us, 50% square wave) to drive the thyristor work.

Schematic circuit diagram

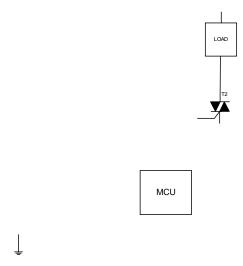

#### 2 Mode 2

The chip uses common power supply mode, when the ZCD is grounded, the chip shields the zero-crossing detection function, and the GATE driver signal is only controlled by the EN signal. When the EN signal output by the MCU to the chip is high, the GATE will output the drive signal (6 cycles of 200us, square wave with 50% duty cycle) and trigger the thyristor work. In order to ensure the full turn-on of the thyristor, the high level maintenance time of the EN is at least longer than the drive signal time of the GATE. When the MCU output EN signal is low, the GATE will stop the output drive signal, and the thyristor will remain closed when the next AC voltage crosses zero.

Schematic circuit diagram

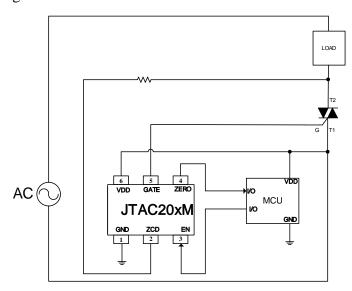

#### 3 Mode 3

The chip uses common power supply mode, ZCD is connected to AC power line or load terminal through resistance. The pin is used for zero-crossing detection. When the chip detection crosses the ZERO, ZERO outputs the zero-crossing signal to the MCU. According to the zero-crossing signal provided by the chip, the MCU can output the EN high level enable signal immediately or after the corresponding delay, and feed back to the chip. At this time, the GATE end of the chip outputs the drive signal (6 cycles of 200us, square wave with 50% duty cycle) and trigger the thyristor work. In order to ensure the full turn-on of the thyristor, the high level maintenance time of the EN is at least longer than the drive signal time of the GATE. When the MCU output EN signal is low, the GATE will stop the output drive signal, and the thyristor will remain closed when the next AC voltage crosses zero.

#### Schematic circuit diagram

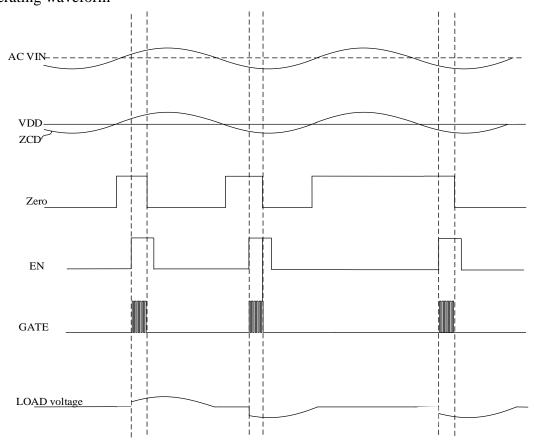

#### Operating waveform

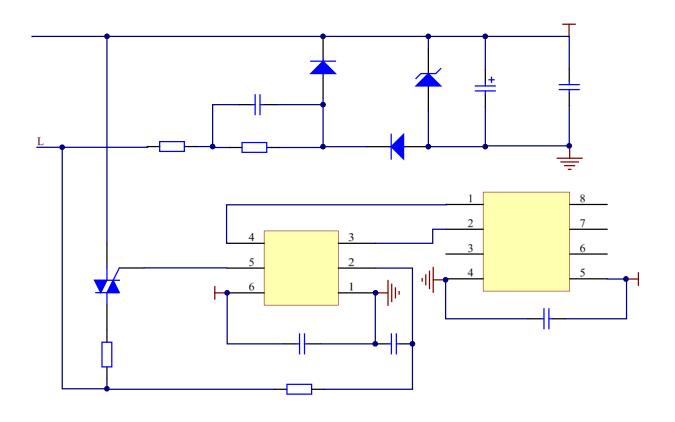

### TYPICAL APPLICATION CIRCUIT

Note: "X" is marked according to the current gear of the GATE actually produced.

| Order code | $\mathbf{I}_{	ext{GATE}}$ | Package  | Base qty.<br>(pcs) | Delivery<br>mode | MPQ<br>(pcs) | MOQ<br>(pcs) |

|------------|---------------------------|----------|--------------------|------------------|--------------|--------------|

| JTAC201M   | A                         | SOT23-6L | 3,000              | Tape and<br>Reel | 30,000       | 120,000      |

| JTAC202M   | В                         | SOT23-6L | 3,000              | Tape and<br>Reel | 30,000       | 120,000      |

| JTAC203M   | C                         | SOT23-6L | 3,000              | Tape and<br>Reel | 30,000       | 120,000      |

| JTAC204M   | D                         | SOT23-6L | 3,000              | Tape and<br>Reel | 30,000       | 120,000      |

| JTAC205M   | E                         | SOT23-6L | 3,000              | Tape and<br>Reel | 30,000       | 120,000      |

# **Document Revision History**

| Date         | Revision | Changes     |

|--------------|----------|-------------|

| May.07, 2023 | 1.0      | Last update |

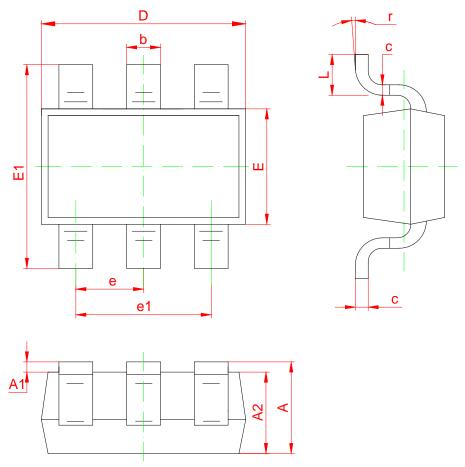

## PACKAGE MECHANICAL DATA

| Symbol | <b>Dimensions In Millimeters</b> |       | <b>Dimensions In Inches</b> |       |  |

|--------|----------------------------------|-------|-----------------------------|-------|--|

|        | Min.                             | Max.  | Min.                        | Max.  |  |

| A      | 1.000                            | 1.300 | 0.039                       | 0.051 |  |

| A1     | 0.000                            | 0.150 | 0.000                       | 0.006 |  |

| A2     | 1.000                            | 1.200 | 0.039                       | 0.047 |  |

| b      | 0.300                            | 0.500 | 0.012                       | 0.020 |  |

| С      | 0.100                            | 0.200 | 0.004                       | 0.008 |  |

| D      | 2.800                            | 3.020 | 0.110                       | 0.119 |  |

| E      | 1.500                            | 1.700 | 0.059                       | 0.067 |  |

| E1     | 2.600                            | 3.000 | 0.102                       | 0.118 |  |

| e      | 0.950 (BSC)                      |       | 0.037                       | (BSC) |  |

| e1     | 1.800                            | 2.000 | 0.071                       | 0.079 |  |

| L      | 0.300                            | 0.600 | 0.012                       | 0.024 |  |

| r      | 0°                               | 8°    | 00                          | 8°    |  |

Information furnished in this document is believed to be accurate and reliable. However, Jiangsu JieJie Microelectronics Co., Ltd. assumes no responsibility for the consequences of use without consideration for such information nor use beyond it. Information mentioned in this document is subject to change without notice, apart from that when an agreement is signed, Jiangsu JieJie complies with the agreement.

Products and information provided in this document have no infringement of patents. Jiangsu JieJie assumes no responsibility for any infringement of other rights of third parties which may result from the use of such products and information. This document supersedes and replaces all information previously supplied.

is a registered trademark of Jiangsu JieJie Microelectronics Co., Ltd. Copyright © 2023 Jiangsu JieJie Microelectronics Co., Ltd. All rights reserved.